研究背景

随着云计算、人工智能、边缘计算等数据密集型计算的发展,高效的内存访问和高性能的计算对高密度片上存储器的需求越来越大。CMOS器件横向尺寸缩放的放缓限制了片上存储器的容量,而片外动态随机存取存储器(DRAM)通常会导致长延迟和高能耗。为提高集成密度,采用2.5维(2.5D)硅中间层和三维(3D)芯片堆叠的先进封装技术已被积极探索。然而,这种集成技术依赖于昂贵的硅通孔(TSVs),并且通常具有大间距,低良率和低可靠性等缺点。单片3D集成系统的特点是逻辑层和存储层的细粒度集成,通过密集的纳米级层间通孔(ILVs)相互连接。因访问内存的延迟和所需的功耗减少,这种技术可以在数据密集型应用场景中减少多达1000倍的能量延迟乘积。这种单片3D集成系统要求在足够低的温度(通常<400 ℃)下制备顶层器件,以确保小的热预算,从而避免影响底层的器件。然而,适合单片3D集成的逻辑和高密度存储的材料和器件仍未得到充分优化,需要谨慎选择和积极探索。由2D半导体制成的晶体管具有自然钝化的表面以减少表面粗糙度散射,并且具有原子级厚度的沟道以增强栅极控制和抑制短沟道效应,这使得它们在3 nm技术节点以下的极小尺寸逻辑器件中非常有前途。此外,尽管2D材料的生长通常在高温下进行,但低转移温度(通常低于150 ℃)使2D材料特别适合垂直异构集成。

成果介绍

有鉴于此,近日,上海交通大学杨睿教授和何哲陟教授(共同通讯作者)等实验展示了原子薄MoS2晶体管和3D垂直阻变式随机存取存储器(VRRAM)的单片3D集成结构,其中MoS2晶体管堆叠在底面和顶面VRRAM之间。整个制备过程是集成友好的(低于300 ℃),测量结果证实了顶层器件的工艺制备并不影响底层器件的特性。MoS2晶体管可以驱动VRRAM的每一层产生四个电阻状态。单片3D结构的电路级建模显示其比平面存储器面积更小,数据传输速度更快,能耗更低。该结构在高能效的3D片上存储系统中具有很高的潜力。文章以“Monolithic 3D integration of 2D transistors and vertical RRAMs in 1T-4R structure for high-density memory”为题发表在著名期刊Nature Communications上。

图文导读

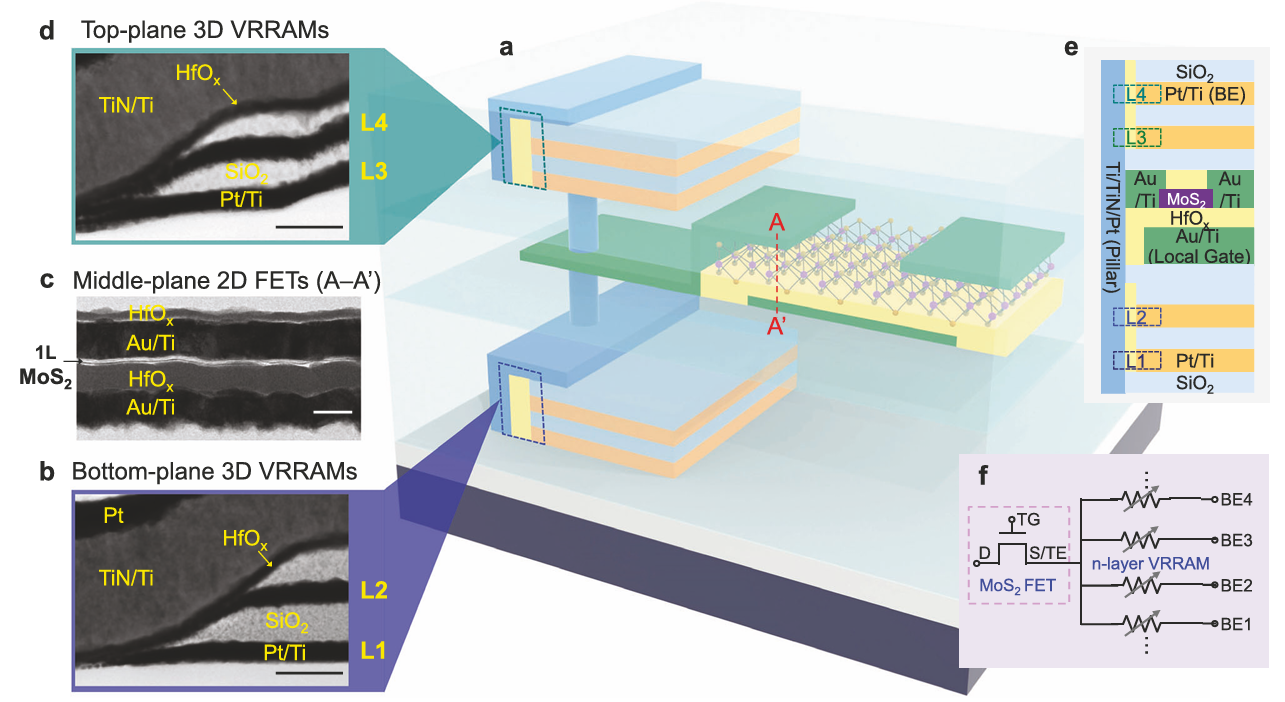

图1. 2D MoS2晶体管和3D VRRAMs单片3D集成的1T-4R结构。(a)1T-4R结构的3D示意图。(b)底层3D VRRAMs (L1和L2)的横截面TEM图。(c)中间层2D MoS2 FET。(d)顶层3D VRRAMs (L3和L4)。(e)结构的横截面示意图。(f)1T-nR结构的等效电路。

为了展示逻辑和存储层的细粒度集成,本文使用HfOx基3D VRRAM作为高密度存储器,由单层MoS2晶体管选择和驱动(图1a)。首先,在底部平面上设计和制备了两层3D VRRAM,然后使用等离子体增强化学气相沉积(PECVD)在300 ℃下生长隔离氧化层。TEM图像证实,第一层(L1)和第二层(L2)忆阻器的工作区域由氮化钛(TiN)/氧化铪(HfOx)/铂(Pt)结构形成,其中TiN为共享柱电极,Pt侧壁为另一个电极(图1b)。然后在中间平面上图案化了具有局部背栅的2D MoS2晶体管,这表明可以在存储器层之上制作额外的晶体管层。虽然在本文的设计中,2D MoS2晶体管主要用于驱动VRRAM,但该工艺具有在不消耗额外芯片面积的情况下提供额外逻辑功能和计算能力的潜力。厘米级单层MoS2由CVD生长,并使用水辅助转移技术在150 ℃下转移,该技术可靠地在具有底层VRRAM,背栅电极和栅极电介质的目标衬底上形成MoS2薄膜。然后将转移的MoS2在280 ℃下真空退火1小时,以提高接触质量并去除吸附物,接着对源极和漏极进行图案化,如横截面TEM图像所示(图1c)。在再次沉积隔离氧化层后,重复之前制备两层3D VRRAM的工艺,得到顶层第3层(L3)和第4层(L4) VRRAM,如横截面TEM图像所示(图1d)。这表明高密度存储器层可以在晶体管层和逻辑层之上进一步图案化。这样,得到了一个2D MoS2晶体管驱动四个VRRAM的单片3D集成结构,即1T-4R结构,层间通孔连接不同的层,如图1e和f所示。这种结构证明了在2D FET层上制备3D VRRAM层以及在3D VRRAM层上制备2D FET层的可行性和通用性。该工艺还具有垂直堆叠更多存储器或晶体管层以实现1T-nR结构的潜力,用于更高的集成密度。

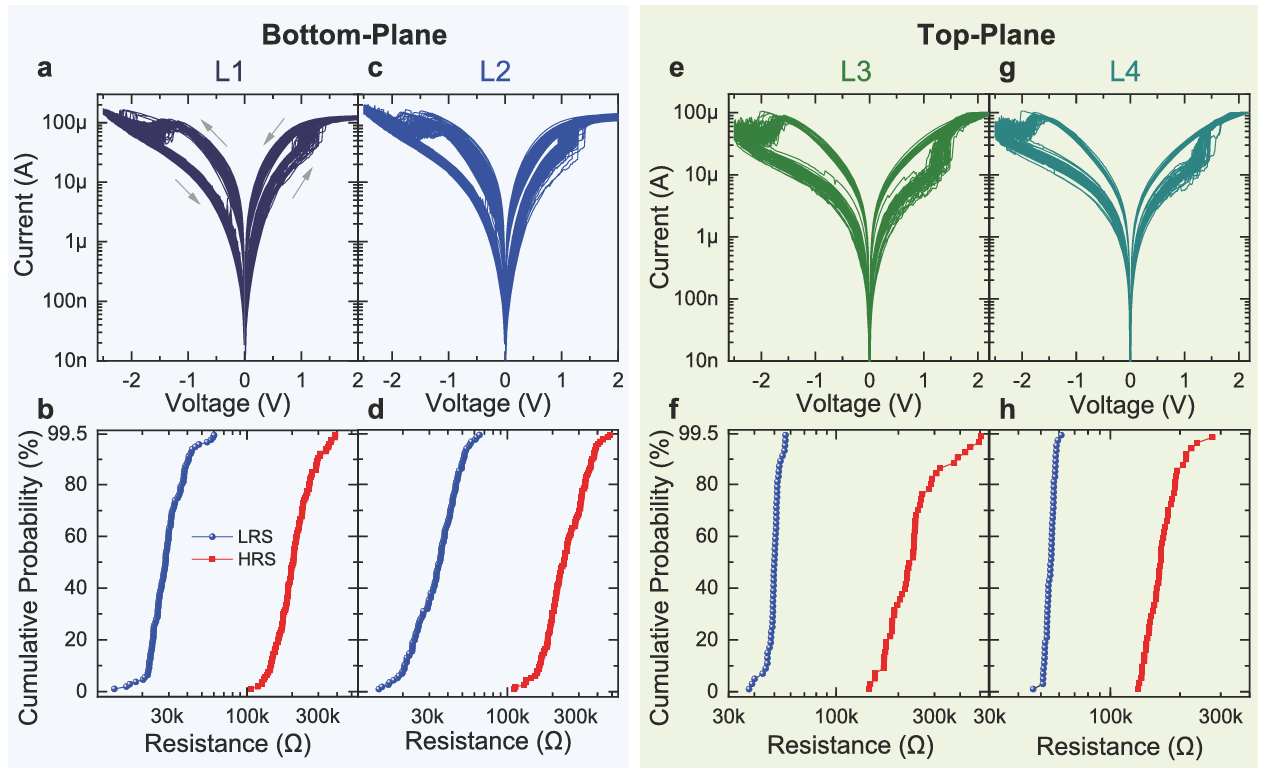

图2. VRRAM各层的电学表征。(a-d)L1和L2 VRRAM的底面双层VRRAM的DC I-V扫描曲线和相应的电阻分布。(e-h)顶部两层VRRAM的测量。

然后,本文对3D VRRAM四层中的每层器件的电学特性进行了表征。在1T-4R器件的测量过程中,通过施加适当的栅极电压(VGS)接通2D MoS2晶体管。将写入/读取电压加到2D MoS2晶体管的漏极上,源极接在VRRAM的柱(顶)电极上,被测VRRAM层的底电极接地,其他层的底电极悬空。在测量VRRAM的每一层时,形成1T-1R结构。3D VRRAM每层的初始导电细丝形成的编写在3.5 V以下进行,随后的直流I-V扫描显示了每层结构的50个翻转周期(图2)。对于底面2层VRRAM(图2a-d)和顶面2层VRRAM(图2e-h),2D MoS2晶体管可以成功驱动VRRAM,并在置位过程中限制电流。四层VRRAM的高电阻状态(HRS)和低电阻状态(LRS)的电阻分布相似,层与层之间具有较高的均一性。

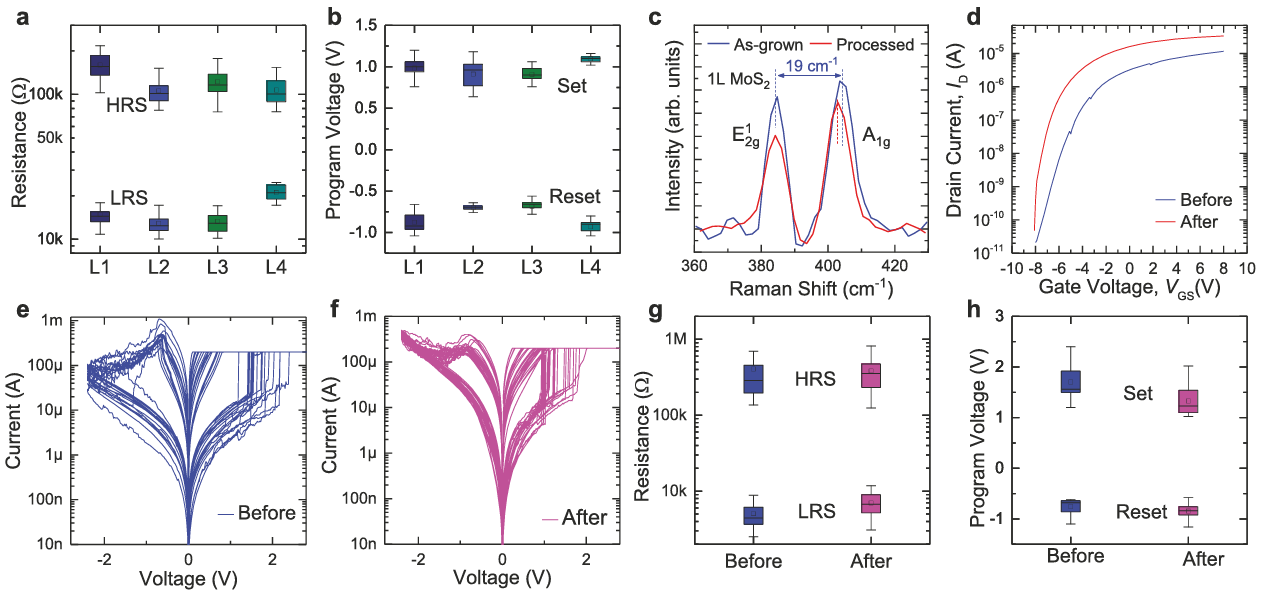

图3. 器件均一性的表征。(a&b)HRS和LRS电阻以及置位和复位电压的测量统计。(c)生长和转移后的单层MoS2的拉曼光谱,显示了A1g峰的拉曼模态软化。(d)2D MoS2 FET在顶层器件制备前后的ID-VGS曲线。(e&f)顶层器件制备前后,同一底层VRRAM器件的电阻开关特性比较。(g&h)顶层器件制备前后,LRS和HRS以及置位和复位电压的统计。

对于垂直堆叠的3D结构,不同层间器件性能的均一性是研究的关键指标。均一性可以从以下几个方面来评估。首先,四层之间的VRRAM器件性质应该是均一的。通过测量多个周期的直流I-V扫描曲线,本文展示了L1至L4 VRRAM的阻值分布和编写电压的均一性(图3a和b)。对于四层VRRAM中的每一层,在保持明显开关阻态的同时,可以获得超过106个脉冲开关周期。第二,顶层器件的制备不会对底层器件产生不利影响。为了验证这一点,本文表征了生长的2D MoS2和转移到目标衬底并覆盖了1.5 nm的AlOx和10 nm的HfOx后MoS2的拉曼光谱,结果显示E2g1模式下的峰位置均匀,A1g拉曼模式下的峰位置软化(图3c)。这表明了来自AlOx层的N型掺杂效应,因为N型掺杂会导致A1g声子模态软化,而E2g1峰位置对掺杂效应相对不敏感。对于生长的MoS2,E2g1和A1g拉曼峰之间的位置差大约为19 cm-1(图3c),这证实了CVD生长的MoS2是单层。2D MoS2 FET的ID-VGS曲线也表明,顶层VRRAM的制备不会对下层的2D MoS2产生不利影响(图3d)。而阈值电压的负向偏移和ID的增加进一步提高了驱动能力,这也可以归因于AlOx隔离层的N型掺杂效应,并且与拉曼表征结果和先前的报道一致。此外,本文测量了 (图3e和f)在制备中间层MoS2 FET和顶面VRRAM前后底层同一VRRAM的直流I-V扫描曲线。阻值和编写电压分布的均一性(图3g和h)表明,在不损害底层器件性能的情况下,垂直堆叠更多晶体管或VRRAM层是可行的。顶层器件制备前后的电阻开关曲线或阻态之间的一些差异可归因于VRRAM固有的循环间变化。这种高均匀性的单片3D结构得益于低制备温度(≤300 ℃)。

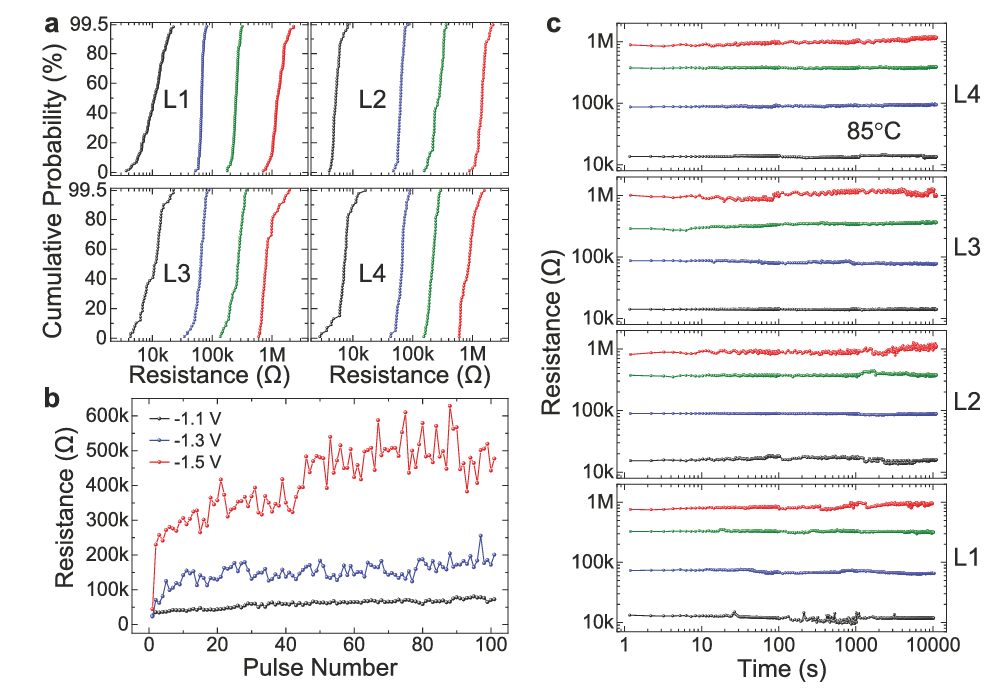

图4. 多阻态VRRAM测量。(a)VRRAM四层的电阻分布,每层可通过调节复位电压实现实现四种电阻态。(b)在相同的电压脉冲幅值下,通过增加复位脉冲数,对电阻进行调制。其中使用的脉冲上升时间为20 ns,下降时间为20 ns,脉宽为60 ns。(c)四层VRRAM在85 ℃下的保持特性测量表明每层VRRAM均显示四种稳定的电阻状态。

本文还验证了制备的3D VRRAM的多阻态编写和读取能力,以得到更高的存储密度。通过在直流电压扫描期间使用不同的复位停止电压,获得了所有4层VRRAM的4个可区分的电阻态,并且每层的4个阻态较为一致(图4a)。进一步通过仔细选择直流扫描电压,可以在相同的4层VRRAM中实现更多的电阻态,最高可达8个不同的阻态,这对于可以容忍不同电阻态之间存在一些分布重叠以及高存储密度等重要的情况非常有用。此外,通过施加越来越多的复位电压脉冲,电阻状态也可以连续调控,电压脉冲越大,电阻值越高,电阻调控范围也越大(图4b)。本文表征了所有4层VRRAM在85 ℃下的电阻保持性能,每层VRRAM都可保持4种稳定的电阻态达10,000 s,中间的电阻变化可忽略不计(图4c)。因此,1T-4R结构总共可实现16种不同的电阻状态。此外,在置位过程中,通过在2D MoS2 FET上施加不同的VGS,也可以获得多个电阻状态,VGS越大,LRS阻值越小,因为在置位过程中,较大的VGS可以允许VRRAM通过更大的电流,导致导电丝具有更大的横向尺寸,这与之前的RRAM模型一致。这两种不同的存储状态调控技术为存储密度增加的多阻态存储提供了更多的可能性。该调控技术可以实现是因为MoS2 FET不仅可以作为接入开关,还可以作为VRRAM置位过程中允许通过的总电流的控制器。这种多级单元和垂直堆叠3D VRRAM的组合展示为超高密度存储器以及计算系统灵活多样的器件性质提供了独特的机会。

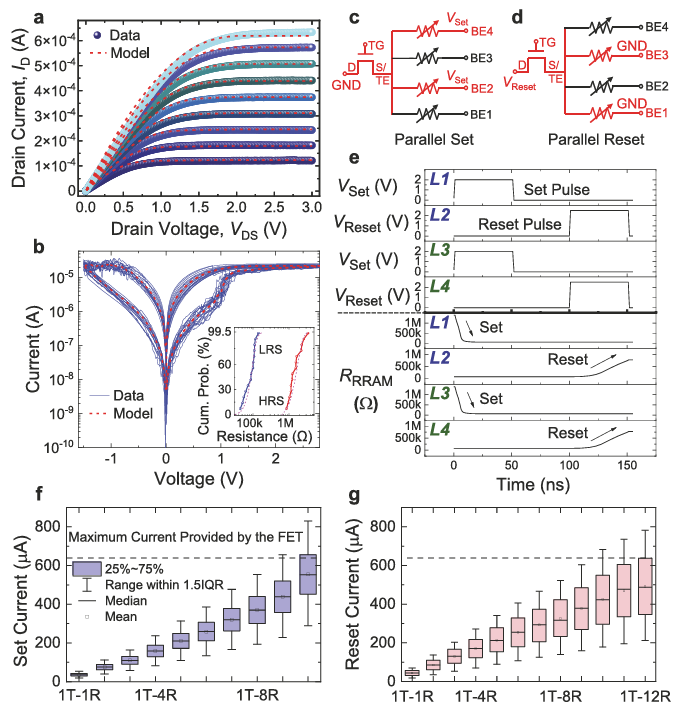

图5. 1T-nR结构的并行编程能力建模。(a)2D MoS2 FET在不同VGS下的ID-VDS特性,并与PTM模型进行了拟合。(b)VRRAM器件的典型电阻开关特性,并与紧凑模型进行了拟合。(c&d)用于并行置位和复位过程的电路示意图。(e)用于编程1T-4R结构的HSPICE瞬态仿真,其中在L1和L3 VRRAM上并行执行了置位操作,然后在L2和L4 VRRAM上并行执行复位操作。(f&g)并行置位和复位操作所需开关电流的仿真。

为了进一步评估该结构的系统级性能增益,基于测量数据,使用HSPICE开发了1T-nR存储单元的器件模型。使用130 nm BSIM4预测技术模型(PTM)拟合MoS2 FET测量的ID-VDS特性(图5a)。通过拟合ID-VDS行为,得到了可用于以下电路级仿真的器件模型。同时,使用RRAM紧凑模型拟合VRRAM单元的置位和复位特性以及HRS和LRS中的阻值分布(图5b)。在MoS2 FET模型和VRRAM模型的基础上,本文进一步模拟了1T-nR方案中VRRAM在同一柱电极上的并行编程。通过控制MoS2晶体管的栅极电压,将设定的置位电流限制在20 μA左右,从而获得更高的LRS阻值。置位/复位功耗分别降至20 μW和30 μW,这有利于提高能效和并行编程能力。通过适当地对FET和VRRAM施加电压偏置,可以在垂直方向上执行并行置位(图5c)或并行复位操作(图5d)。图5e中的HSPICE瞬态仿真演示了一个代表性的情况,即L1和L3 VRRAM首先并行置位为LRS,然后L2和L4 VRRAM并行复位为HRS。VRRAM的电阻状态也会影响并行驱动能力。在HRS电阻固定的情况下,当存在非理想效应时,较大的LRS阻值可能导致LRS和HRS重叠,从而产生误码。同时,LRS的电阻值过低会增加所需的复位电流。随着并行编程的VRRAM数量的增加,可以通过提高MoS2 FET上的栅极电压以扩大驱动电流。

垂直方向上的并行编程能力取决于MoS2 FET提供的驱动电流和VRRAM器件之间的本征波动。首先对在置位(图5f)和复位(图5g)过程中同时切换不同数量VRRAM层所需的驱动电流进行建模,并与MoS2 FET可以提供的电流进行比较。考虑到VRRAM的电阻波动,对于置位过程,MoS2 FET可以驱动多达8层的VRRAM;对于复位过程,它可以在1T-nR配置中并行驱动多达9层VRRAM。通过降低接触电阻、使用具有更高载流子迁移率的2D半导体或通过堆叠2D纳米片构建全环绕栅极晶体管,可以进一步提高并行驱动能力。

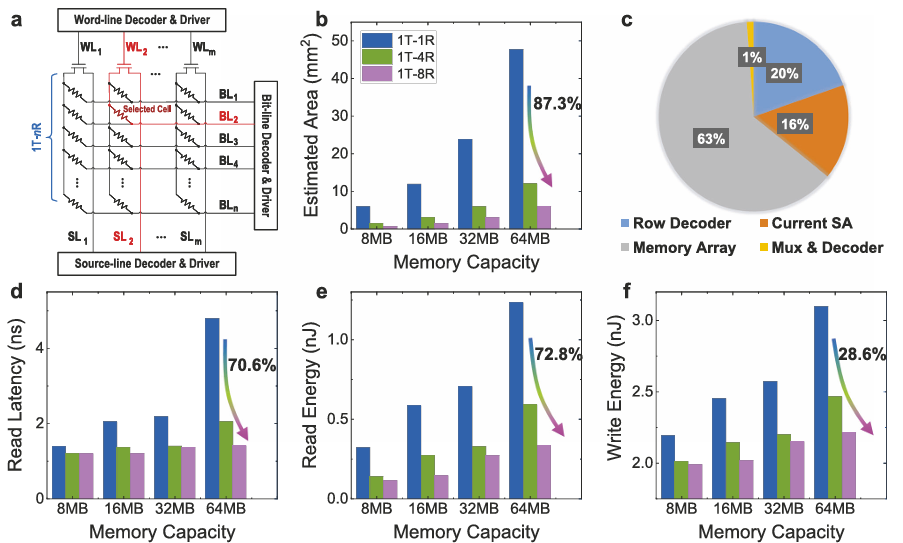

图6. 基于单片3D集成的MoS2 FET和VRRAM的存储系统性能仿真。(a)NVSim中1T-nR结构的电路仿真框架。(b)不同容量配置(8-64 MB)下,使用1T-1R、1T-4R和1T-8R结构的存储系统的估计面积比较。(c)1024×1024 1T-4R VRRAM阵列及其外围电路的面积分布。(d-f)1T-1R、1T-4R和1T-8R结构的读取延时、读取功耗和写入功耗耗比较。

为了揭示在存储系统中使用这种1T-nR单片3D结构的增益,本文使用NVSim(非易失性存储器的电路级性能仿真工具)在65 nm节点上进行电路级建模。要评估的1T-nR电路和架构如图6a所示。根据测量到的器件参数,在NVSim中进行架构建模,以获得不同内存容量(8-64 MB)的存储阵列的面积、延迟和功耗,并比较1T-1R和1T-nR配置的性能。使用1T-nR而不是1T-1R配置的一个直接优势是,在相同的占用空间下具有更高的存储密度。文中对于具有1024×1024存储单元和必要外围电路的存储阵列,比较了1T-1R和1T-nR配置的存储阵列面积,结果表明在相同存储容量下,1T-4R和1T-8R配置的存储阵列面积分别比1T-1R配置减少了74.8%和87.3%(图6b)。这是由于1T-nR结构有效地利用垂直方向进行堆叠。如图6c所示,存储阵列占整个系统的大部分面积,对于基于1T-4R单元的1024×1024 VRRAM阵列,该面积占比高达63%。与传统的1T-1R设计相比,额外外设分别只占1T-4R和1T-8R阵列面积开销的0.8%和1.6%。采用1T-nR 3D堆叠技术显著减小了片上存储面积,可以有效地提高片上存储容量,降低制备成本。除了减少的面积外,还分析了1T-nR结构在读取延迟和读写功耗方面的其他好处(图6d-f)。这种优势起源于通过垂直层间通孔而不是较长平面路径传输信号/数据,传输长度大大减少,以及从输入/输出(I/O)端口到存储器阵列的路径减少,因为与具有相同容量的1T-1R阵列相比,1T-nR阵列的芯片尺寸减小了。对于1T-1R和1T-nR结构,本文通过使用固定的1024个I/O端口并行读取和写入相同的数据来进行比较。与1T-1R结构相比,读取延迟有了显著的改善,1T-4R和1T-8R结构的读取延迟分别降低了57.2%和70.6%(图6d)。与读取延迟降低一致,对于1T-8R结构,读取功耗降低了高达72.8%(图6e),写入功耗也降低了高达28.6%(图6f)。写入延迟几乎没有改善,因为它在仿真中由50 ns置位/复位写入脉冲信号主导。通过堆叠更多的VRRAM层和更高的内存容量,可以在固定存储容量大小的情况下进一步减少面积、延迟和能耗。

总结与展望

本文展示了2D MoS2 FET和3D VRRAM的单片3D集成,形成具有五个器件层的1T-4R结构,可以实现高密度和低功耗的片上存储器。这种集成结构是在300 ℃以下制造的,这使得顶层器件可以垂直堆叠,而不影响底层器件的性能。测量结果显示了VRRAM在不同器件层之间的性能均一性,以及在顶层器件制备前后MoS2 FET和VRRAM特性的一致性。低制备温度允许晶体管层和存储层以任意顺序连续垂直堆叠。每个VRRAM单元可以被编程为四个稳定的电阻态,从而进一步提高了存储密度。仿真结果表明,与1T-1R结构相比,1T-nR结构可以大大减少芯片面积、读取延迟和读写能耗。具有高开/关比的2D MoS2晶体管可以有效地抑制漏电流,并允许向大规模存储阵列扩展。这种单片3D集成为逻辑和高密度片上存储器的细粒度集成铺平了道路,从而实现高带宽和低功耗存储和计算系统。

文献信息

Monolithic 3D integration of 2D transistors and vertical RRAMs in 1T-4R structure for high-density memory

(Nat. Commun., 2023, DOI:10.1038/s41467-023-41736-2)